Autor: Pablo Sánchez Cuevas

Tutor: Fernando Díaz del Rio

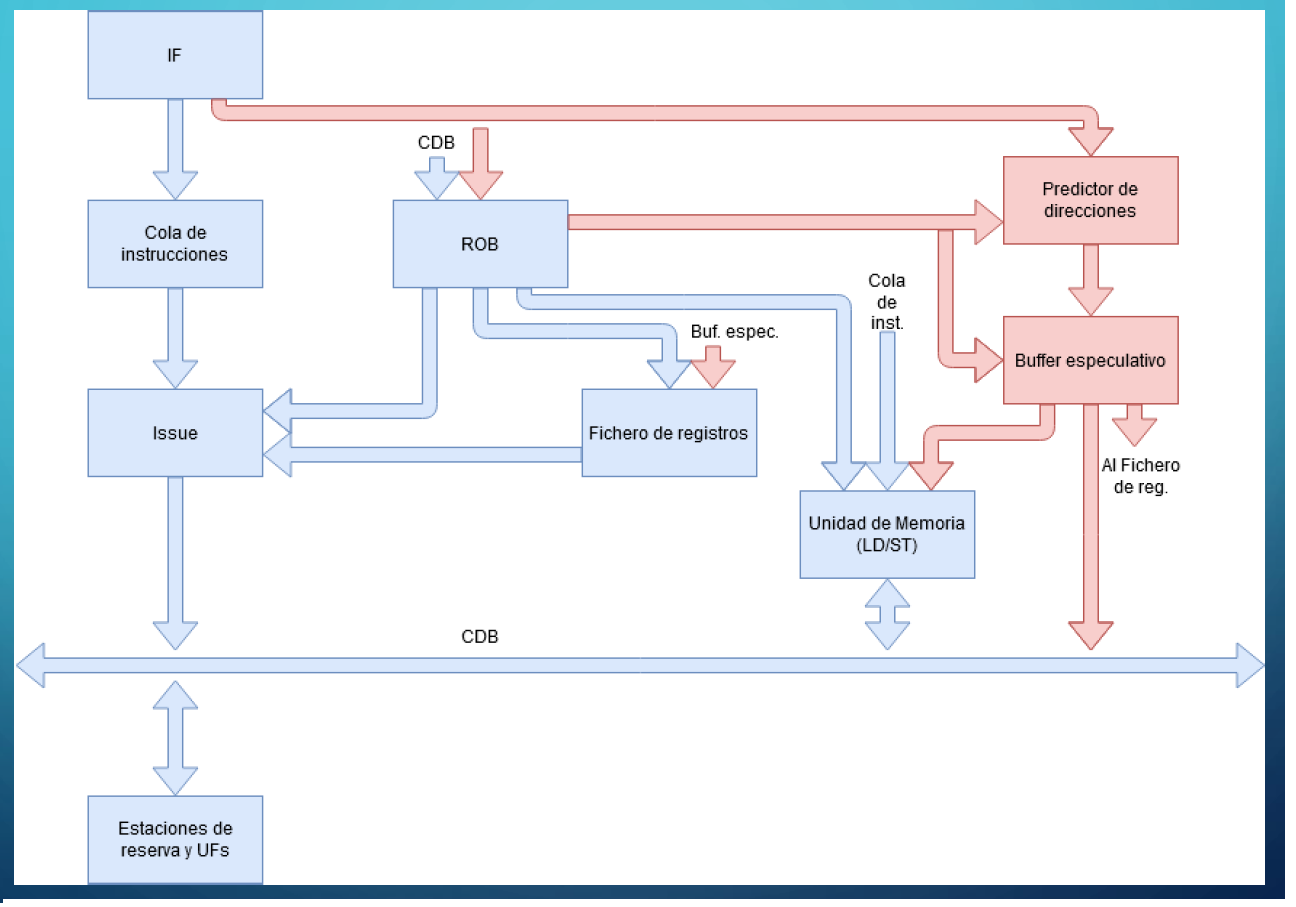

Resumen: En este trabajo se explora el estado del arte de la Predicción de Valores (Value Prediction) en la microarquitectura de una CPU superescalar con especulación dinámica y, con un mayor foco, la Predicción de Direcciones de memoria (Address Prediction).

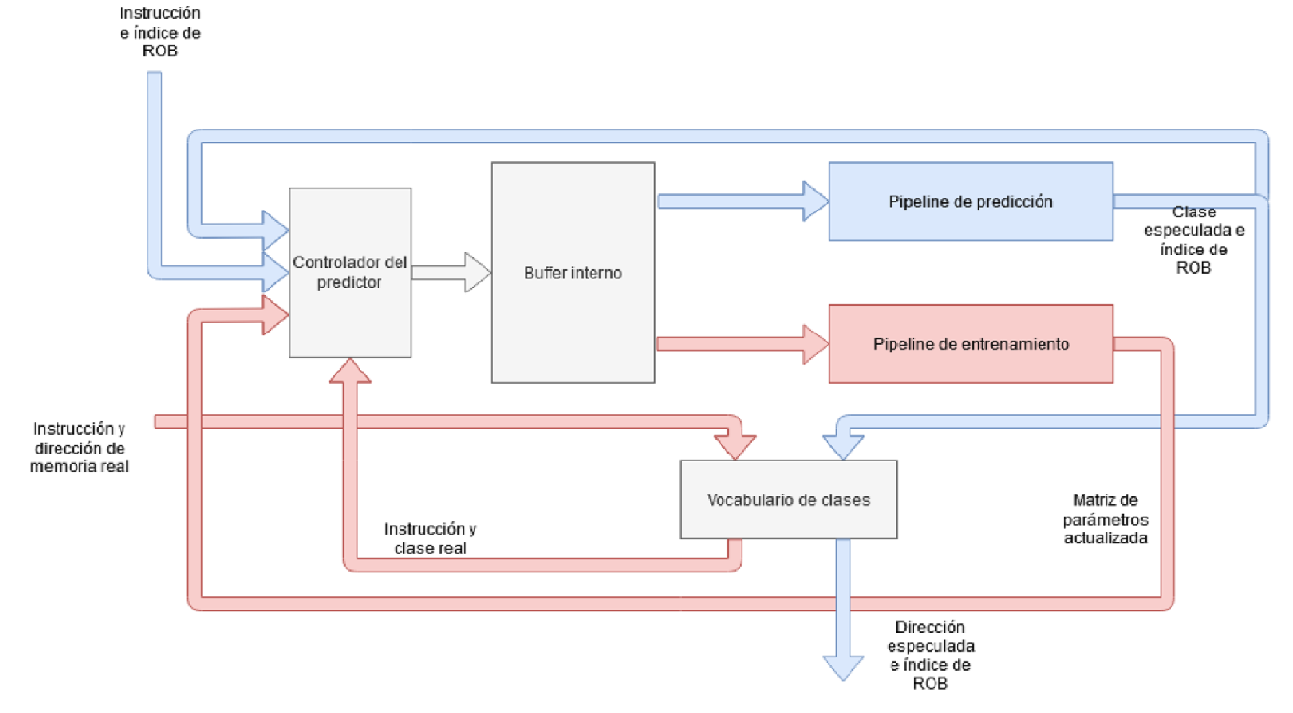

A su vez, se introducen las diferentes técnicas clásicas que abordan dichas estrategias de microarquitectura, además de recorrer aquellas aproximaciones noveles que se están llevando a cabo en los últimos años en el campo de las Redes Neuronales. En este contexto, se propone un modelo de arquitectura hardware que pudiera dar solución a este problema y se evalúan las diferentes restricciones que conlleva.

Posteriormente, se parte de dos algoritmos que representan, debido a la forma de sus patrones de acceso a memoria, un caso favorable y un caso desfavorable respectivamente: un bucle SAXPY y un algoritmo de Etiquetación de Componentes Conexas (Connected Components Labeling).

De estos se obtienen sus trazas de accesos a memoria y se analiza el patrón que subyace en las direcciones de memoria obtenidas. Finalmente se proponen diferentes arquitecturas y modelos de Machine Learning y se evalúan sus resultados para las trazas anteriores.

Calificación: Matrícula de Honor